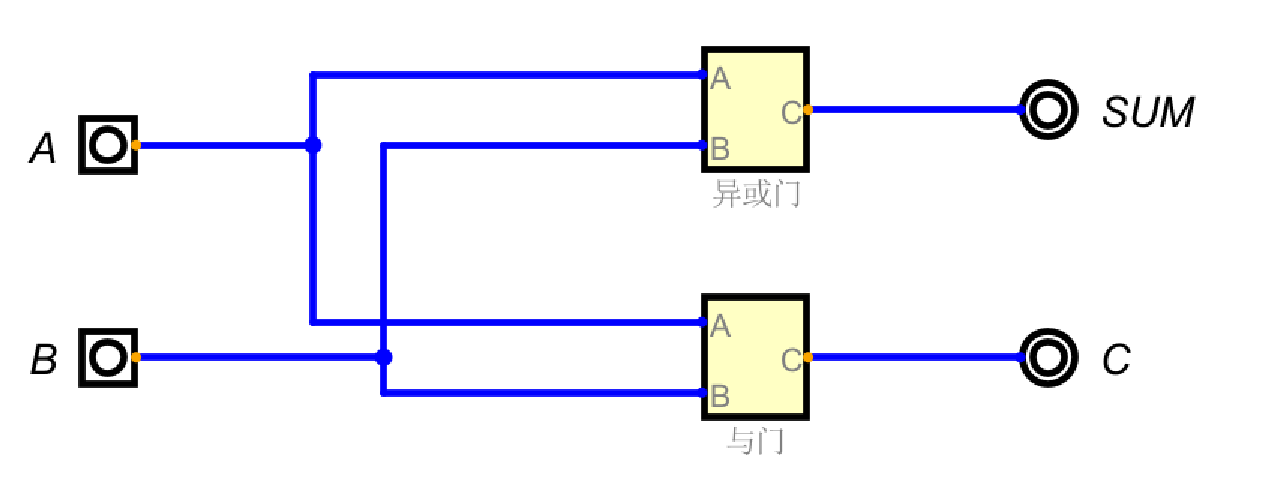

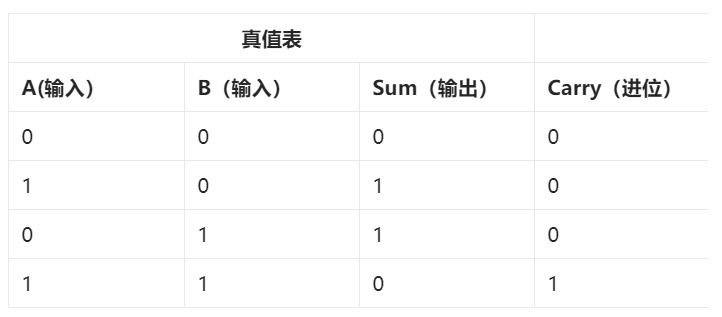

半加器

半加器是一种能够对两个一位二进制数进行相加并输出结果的逻辑门电路。它只能处理两个输入位(被加数和加数),不考虑低位进位。

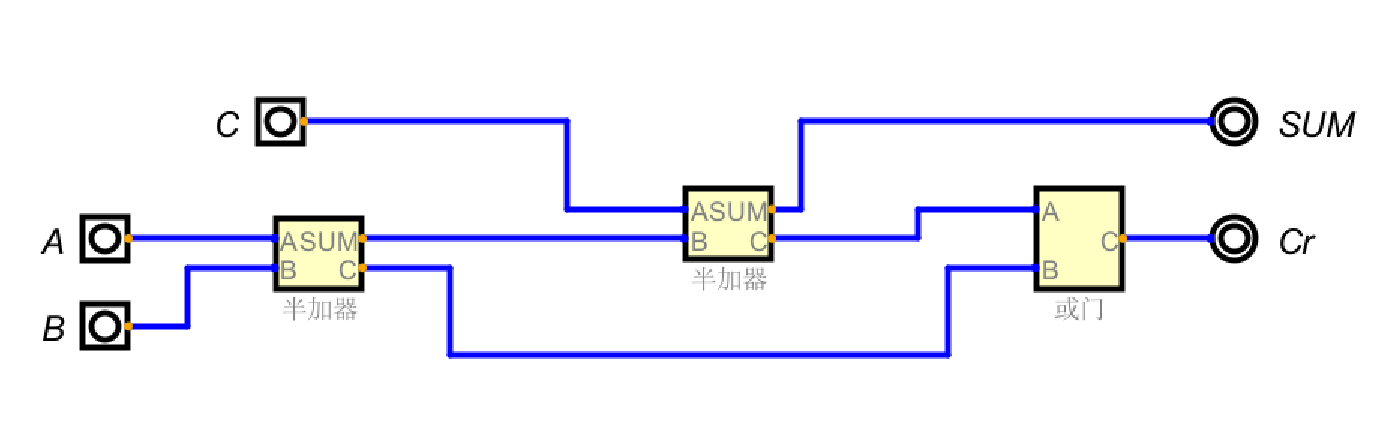

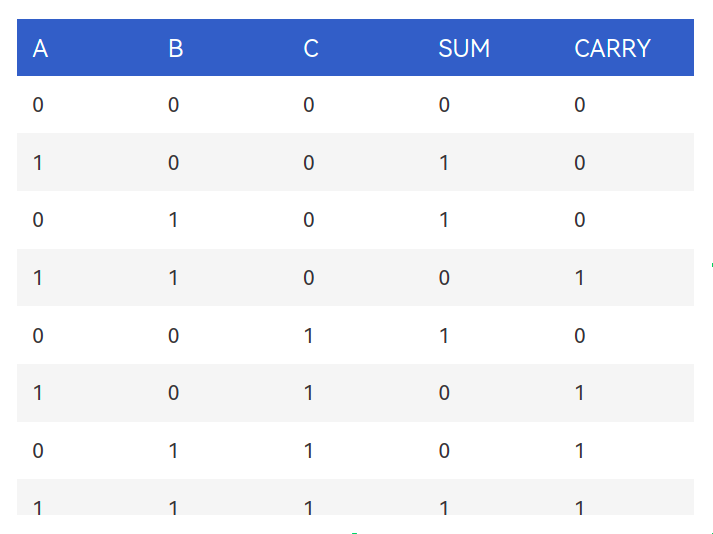

全加器

全加器(Full-Adder)是一种能够处理两个一位二进制数以及它们之间可能产生的进位的加法器;

在计算机中,全加器是算术逻辑单元(ALU)的重要组成部分,用于执行加法、减法等算术运算(在计算机中所谓的减法、称法、除法都是通过加法来实现的);

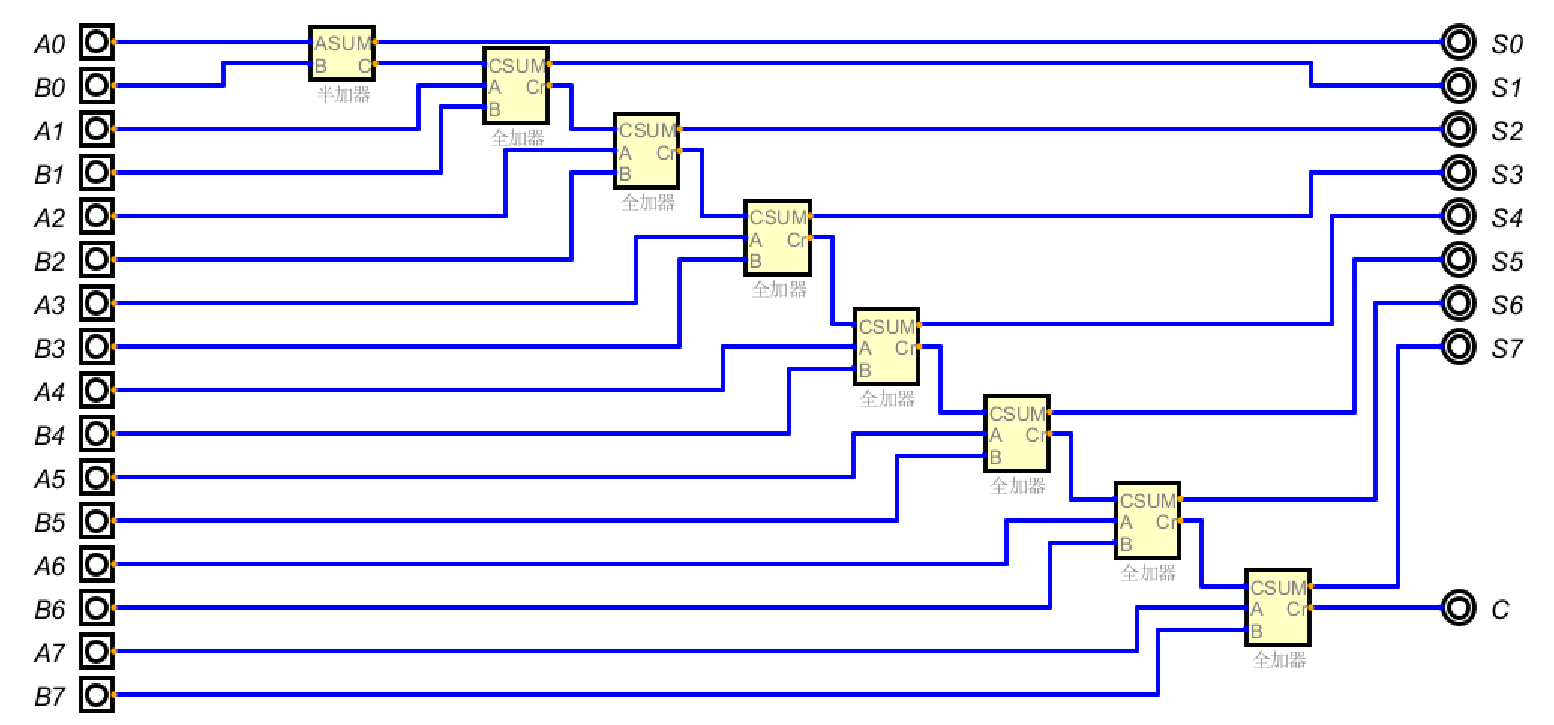

八位二进制加法器

八位二进制加法器是一种数字电路,用于将两个八位的二进制数相加,并产生一个八位的和以及一个进位输出(通常称为溢出位或最高位进位)。

八位二进制加法器能够执行从0到255之间的任何两个数的加法,产生从0到510(包括溢出情况)的结果。如果结果小于或等于255,则溢出位为0;如果结果大于255,则溢出位为1,表示实际结果需要模256处理(在计算机科学中,这通常意味着忽略溢出位,只考虑最低的八位)。

由上述可以看出,任意位数的加法器都只需要对应个数的全加器及可实现(如:16位加法器之只需要一个半加器和15个全加器。)

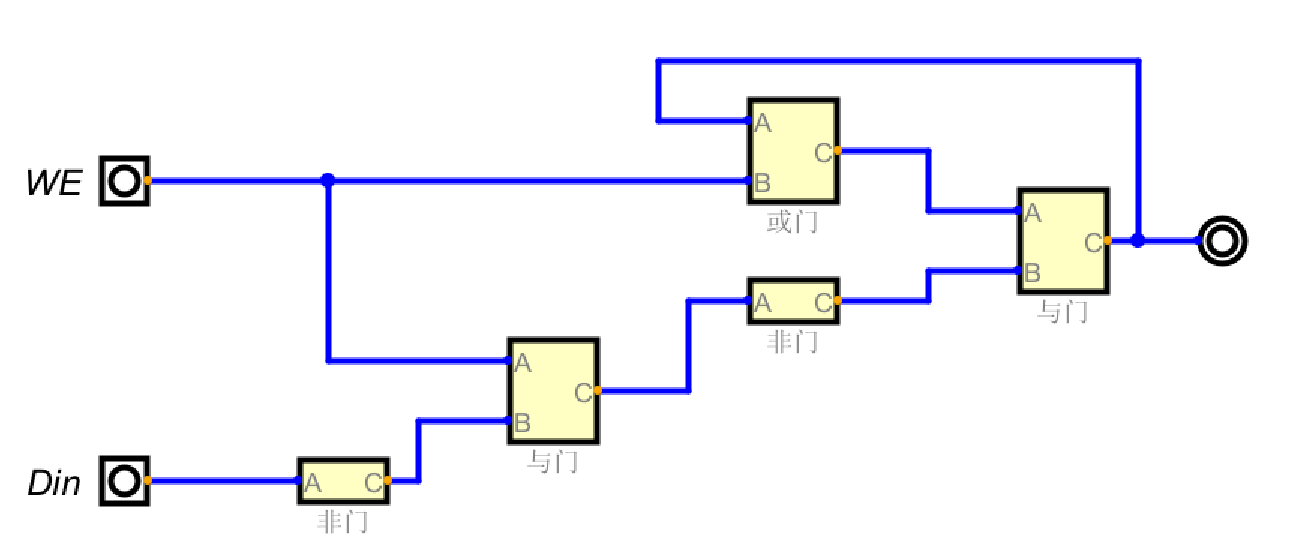

锁存器

可记忆数据的电路

锁存器的工作原理基于电平控制数据的输入。它通常包括锁存控制信号输入端(如使能端WE)、数据输入端(Din)和数据输出端(Q)。当锁存控制信号有效时(如使能端WE为高电平或低电平,具体取决于锁存器的类型),数据输入端(Din)的状态被锁存到输出端Q,并保持不变,直到下一个锁存信号到来。

锁存器可以将数据暂存起来,等待后续处理,从而起到缓存的作用。